Logički sklopovi

| Sitio: | CARNET - Arhiva 2021 Loomen |

| Curso: | Digitalna logika |

| Libro: | Logički sklopovi |

| Imprimido por: | Invitado |

| Día: | Saturday, 21 de March de 2026, 06:52 |

Tabla de contenidos

- 1. Osnovni logički sklopovi

- 1.1. Logički sklop I realiziran preko elektroničkih komponenata

- 1.2. Naponska stanja logičkog sklopa I

- 1.3. Zabrana vođenja logičkog sklopa I

- 1.4. Logički sklop ILI realiziran preko elektroničkih komponenata

- 1.5. Naponska stanja logičkog sklopa ILI

- 1.6. Zabrana vođenja logičkog sklopa ILI

- 1.7. Logički sklop NE realiziran preko elektroničkih komponenata

- 1.8. Naponska stanja logičkog sklopa NE

- 1.9. Logički sklop NI realiziran preko elektroničkih komponenata

- 1.10. Naponska stanja logičkog sklopa NI

- 1.11. Zabrana vođenja logičkog sklopa NI

- 1.12. Logički sklop NILI realiziran preko elektroničkih komponenata

- 1.13. Naponska stanja logičkog sklopa NILI

- 1.14. Zabrana vođenja logičkog sklopa NILI

- 1.15. Video osnovni logički sklopovi

- 2. Složeni logički sklopovi

1. Osnovni logički sklopovi

Logički sklop I => množenje

Logički sklop ILI => zbrajanje

Logički sklop NE => negacija

Logički sklop NI => negirano množenje

Logički sklop NILI => negirano zbrajanje

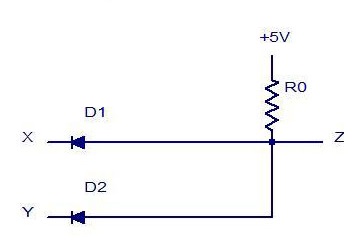

1.1. Logički sklop I realiziran preko elektroničkih komponenata

Dolje je prikazana shema logičkog sklopa I realiziranog preko elektroničkih komponenata.

Katode dioda D1 i D2 su spojene na ulaze (X i Y) a njihove anode su spojene na izvor napajanja (5 V).

Kada se na bilo koji ulaz dovede napon stanja logičke 0 (0 V) dioda vodi jer je njena anoda spojena na pozitivan napon, a katoda na masu. Napon koji se može izmjeriti na izlazu Z je jednak padu napona na diodi. S obzirom da je napon vođenja diode nizak ovaj napon je ekvivalentan stanju logičke 0.

Kada se na ulaze dovede napon stanja logičke 1 (5 V) diode ne vode jer je razlika napona između anode i katode preniska da bi diode provele. Na taj način diode predstavljaju prekid puta prema masi. Napon napajanja je direktno spojen na izlaz Z. Napon napajanja je ekvivalentan stanju logičke 1.

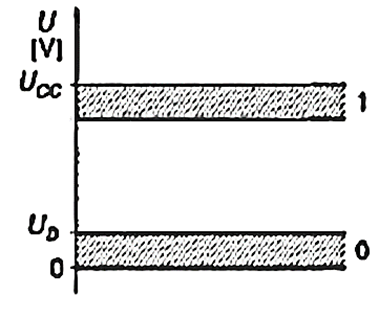

1.2. Naponska stanja logičkog sklopa I

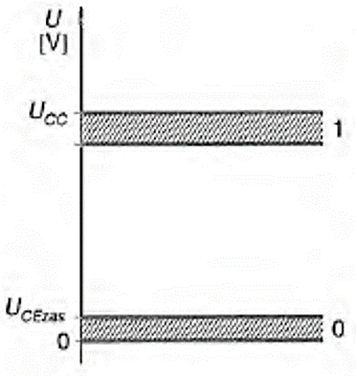

Kao što je rečeno u prethodnom potpoglavlju naponsko stanje 0 je stanje kada su diode u stanju vođenja te ja napon koji se može izmjeriti na izlazu jednak padu napona na diodi u stanju vođenja (Ud).

Naponsko stanje 1 je stanje kada su diode u stanju zapiranja te je na izlaz spojen napon napajanja (Ucc)

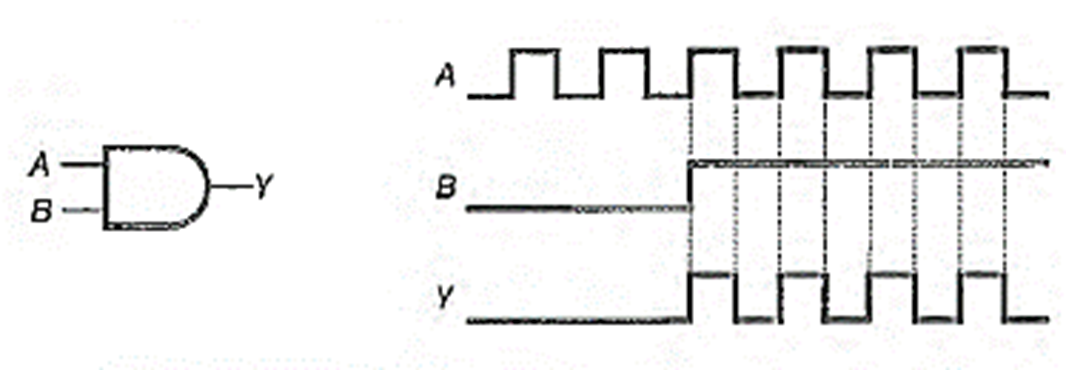

1.3. Zabrana vođenja logičkog sklopa I

Kada na jedan od ulaza sklopa I dovedemo stanje logičke 0 izlaz će biti u stanju logičke 0. Potpuno je svejedno što stavljamo na ulaz A jer je u tom slučaju izlaz uvijek u stanju 0. To stanje se naziva zabrana vođenja preko ulaza B. Kada se ulaz B postavi u stanje 1 on dopušta vođenje ulazu A.

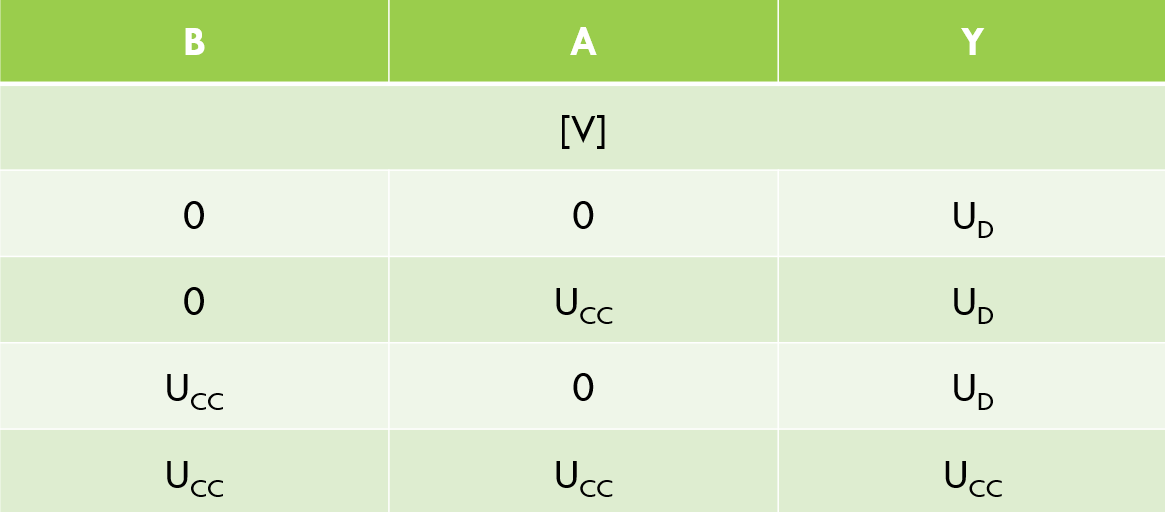

1.4. Logički sklop ILI realiziran preko elektroničkih komponenata

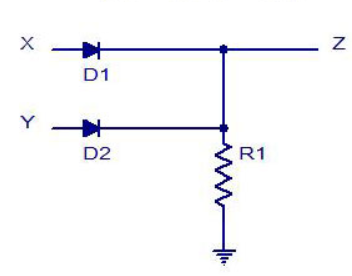

Dolje je prikazana shema logičkog sklopa ILI realiziranog preko elektroničkih komponenata.

Anodedioda D1 i D2 su spojene na ulaze (X i Y) a njihove anode su spojene na izvor napajanja (5 V).

Kada se na ulaze dovede napon stanja logičke 0 (0 V) diode ne vode jer jer su njihove anode i katode spojene na masu. Izlaz Z je direktno spojen na masu što je ekvivalent naponu logičke 0.

Kada se na ulaz dovede napon stanja logičke 1 (5 V) dioda vode. Napon spojen na izlaz Z je jednak naponu napajanja umanjen za pad napona. Napon je ekvivalentan stanju logičke 1.

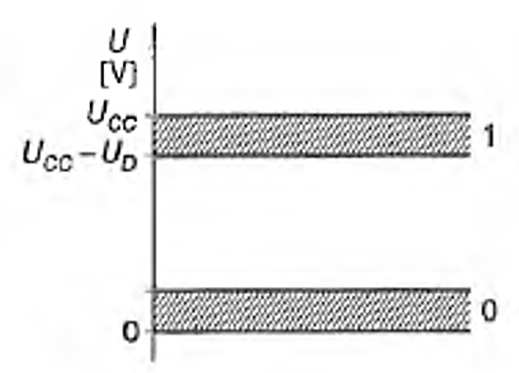

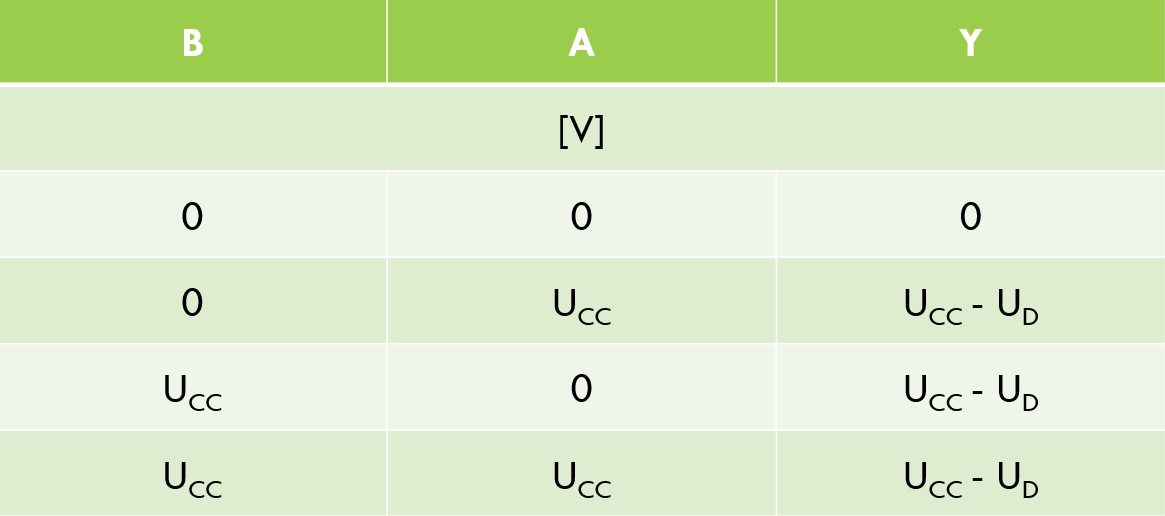

1.5. Naponska stanja logičkog sklopa ILI

Kao što je rečeno u prethodnom potpoglavlju naponsko stanje 0 je stanje kada su diode u stanju zapiranja te je izlaz spojen na masu (0).

Naponsko stanje 1 je stanje kada su diode u stanju vođenja te je na izlaz spojen napon napajanja umanjen za pad napona na diodi (Ucc - Ud)

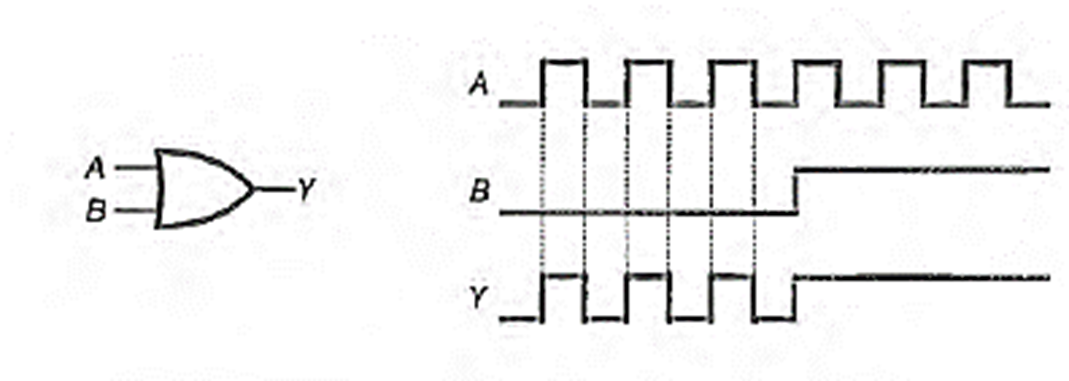

1.6. Zabrana vođenja logičkog sklopa ILI

Kada na jedan od ulaza sklopa I dovedemo stanje logičke 1 izlaz će biti u

stanju logičke 1. Potpuno je svejedno što stavljamo na ulaz A jer je u

tom slučaju izlaz uvijek u stanju 1. To stanje se naziva zabrana vođenja

preko ulaza B. Kada se ulaz B postavi u stanje 0 on dopušta vođenje

ulazu A.

1.7. Logički sklop NE realiziran preko elektroničkih komponenata

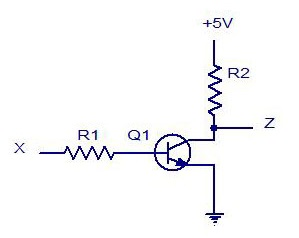

Dolje je prikazana shema logičkog sklopa NE realiziranog preko elektroničkih komponenata.

Ulaz X je spojen na bazu tranzistora te preko njega upravljamo vođenjem tranzistora. Na kolektor tranzistora je spojen napon napajanja, a na emiter je spojena masa.

Kada je na X doveden napon koji predstavlja stanje logičke 1 tranzistor Q1 vodi i napon napajanja provodi direktno na masu. Na izlazu Z se može izmjeriti napon koji odgovara naponu između kolektora i emitera tranzistora u zasičenju. Taj napon je ekvivalentan stanju logičke 0.

Kada je na X doveden napon koji predstavlja stanje logičke 0 tranzistor Q1 je u stanju zapiranja pa predstavlja prekid u krugu. Ucc je direktno spojen na Izlaz Z te je ekvivalentan stanju logičke 1.

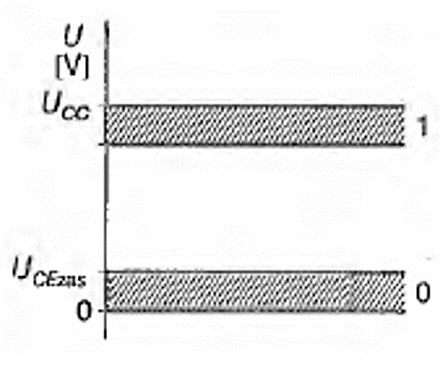

1.8. Naponska stanja logičkog sklopa NE

Kao što je rečeno u

prethodnom potpoglavlju naponsko stanje 0 je stanje kada je tranzistor u stanju zasičenja. Na izlazu se može izmjeriti napon između kolektora i emitera tranzistora u zasičenju.

Naponsko

stanje 1 je stanje kada je tranzistor u stanju zapiranja te je na izlaz spojen

napon napajanja Ucc

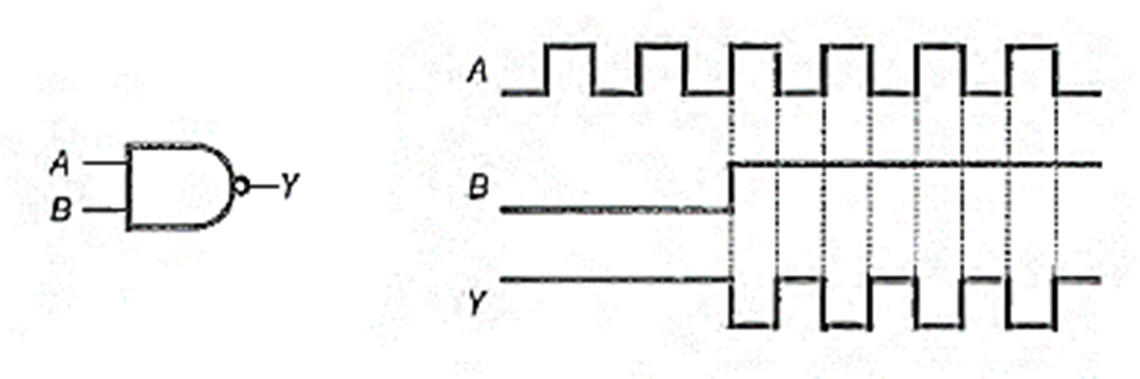

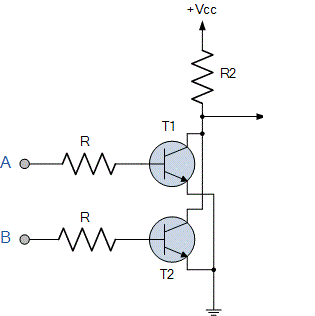

1.9. Logički sklop NI realiziran preko elektroničkih komponenata

Dolje je prikazana shema logičkog sklopa NI realiziranog preko elektroničkih komponenata.

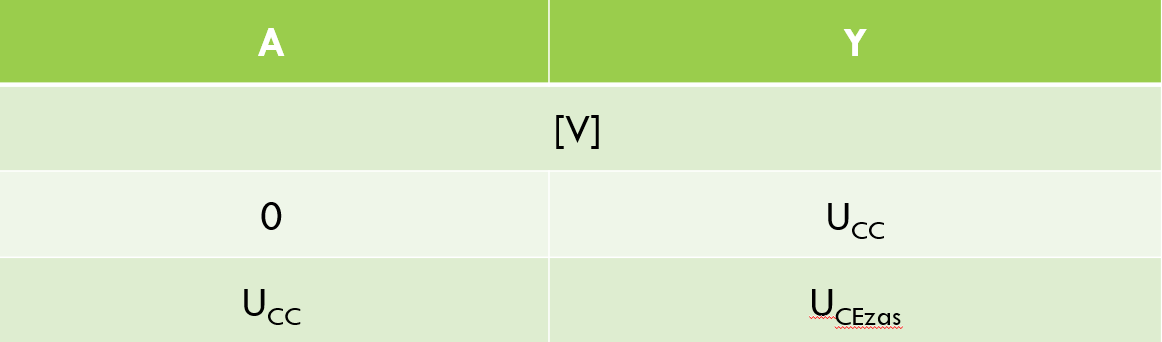

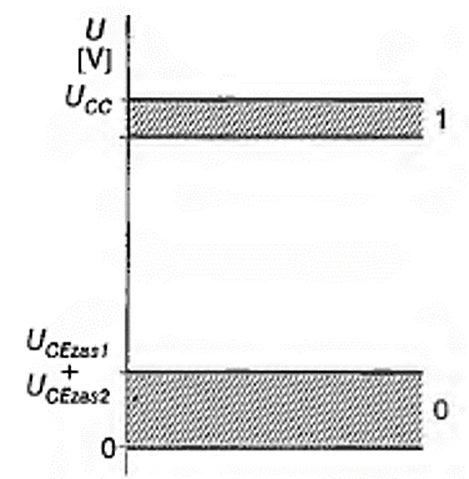

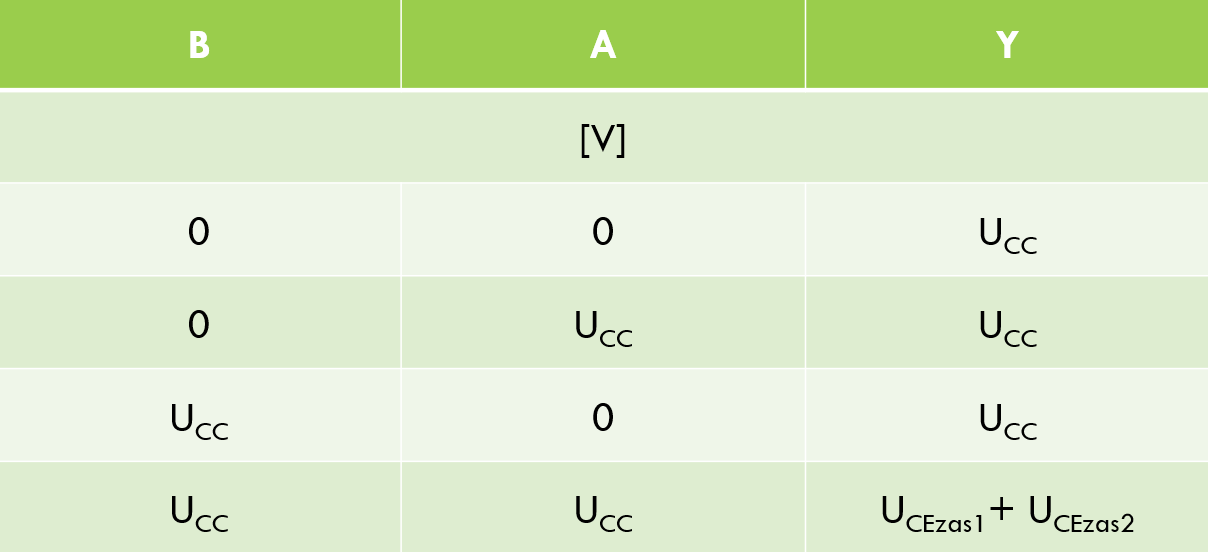

1.10. Naponska stanja logičkog sklopa NI

Kao što je rečeno u prethodnom potpoglavlju naponsko stanje 0 je stanje kada su oba tranzistora u stanju zasičenja. Na izlazu se može izmjeriti zbroj napona između kolektora i emitera oba tranzistora u zasičenju.

Naponsko stanje 1 je stanje kada je bilo koji tranzistor u stanju zapiranja te je na izlaz spojen napon napajanja Ucc.

1.11. Zabrana vođenja logičkog sklopa NI

Kada na jedan od ulaza sklopa I dovedemo stanje logičke 0 izlaz će biti u stanju logičke 1. Potpuno je svejedno što stavljamo na ulaz A jer je u tom slučaju izlaz uvijek u stanju 1. To stanje se naziva zabrana vođenja preko ulaza B. Kada se ulaz B postavi u stanje 1 on dopušta vođenje ulazu A.

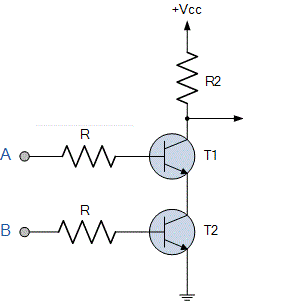

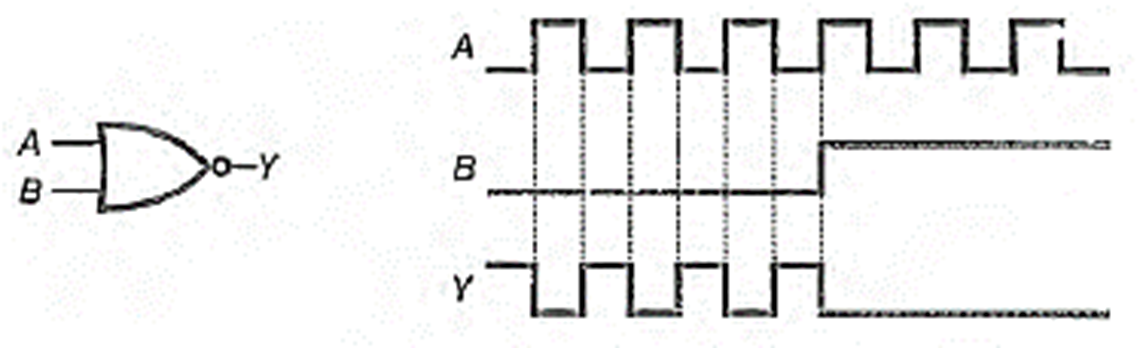

1.12. Logički sklop NILI realiziran preko elektroničkih komponenata

Dolje je prikazana shema logičkog sklopa NILI realiziranog preko elektroničkih komponenata.

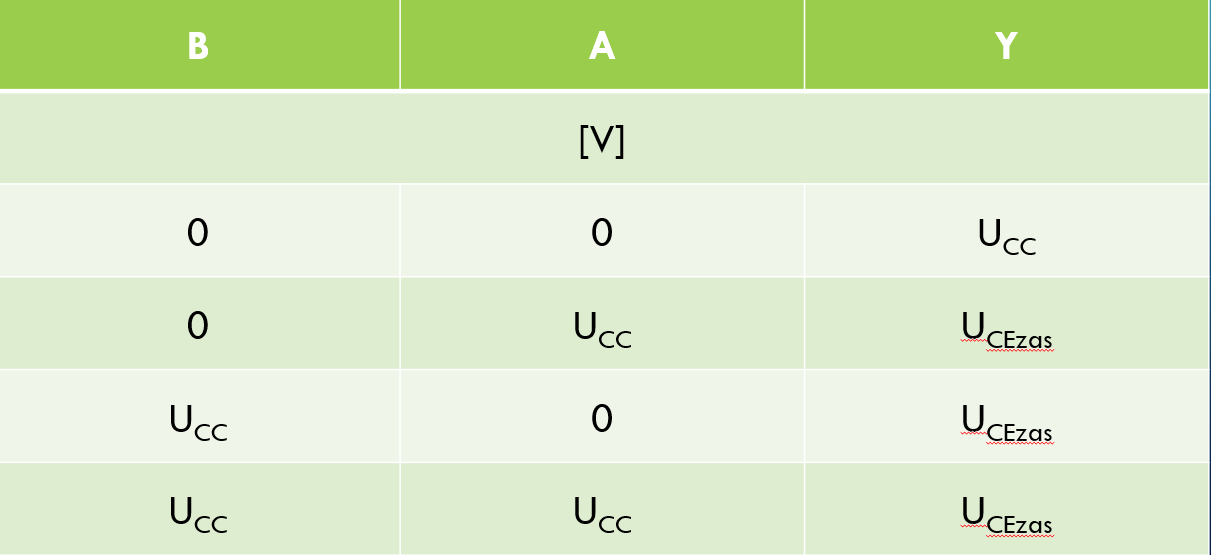

1.13. Naponska stanja logičkog sklopa NILI

Kao što je rečeno u prethodnom potpoglavlju naponsko stanje 0 je stanje kada je bilo koji tranzistor u stanju zasičenja. Na izlazu se može izmjeriti napon između kolektora i emitera tranzistora u zasičenju.

Naponsko stanje 1 je stanje kada su oba tranzistora u stanju zapiranja te je na izlaz spojen napon napajanja Ucc

1.14. Zabrana vođenja logičkog sklopa NILI

Kada na jedan od ulaza sklopa I dovedemo stanje logičke 1 izlaz će biti u stanju logičke 0. Potpuno je svejedno što stavljamo na ulaz A jer je u tom slučaju izlaz uvijek u stanju 0. To stanje se naziva zabrana vođenja preko ulaza B. Kada se ulaz B postavi u stanje 0 on dopušta vođenje ulazu A.

1.15. Video osnovni logički sklopovi

2. Složeni logički sklopovi

Minterm

Maksterm

2.1. Minterm

Ovakva logička operacija, koja na izlazu daje jedinicu samo za jednu ulaznu kombinaciju, a za sve ostale ulazne kombinacije na izlazu je logička nula, naziva se minterm jer je broj jedinica na izlazu minimalan.

2.2. Maksterm

Ovakva logička operacija, koja na izlazu daje nulu samo za jednu ulaznu kombinaciju, a za sve ostale ulazne kombinacije na izlazu je logička jedinica, naziva se maksterm jer je broj jedinica na izlazu maksimalan.