TTL i CMOS

| Sjedište: | CARNET - Arhiva 2021 Loomen |

| E-kolegij: | Digitalna logika |

| Knjiga: | TTL i CMOS |

| Otisnuo/la: | Gost (anonimni korisnik) |

| Datum: | nedjelja, 29. ožujka 2026., 08:07 |

Sadržaj

- 1. Karakteristične veličine integrianih digitalnih sklopova

- 2. Integrirani sklopovi skupina TTL, MOS i CMOS

- 2.1. Osnovni sklop skupine TTL (Ulazi u stanju 0)

- 2.2. Nadomjesna shema kada su ulazi u stanju 0

- 2.3. Osnovni sklop skupine TTL (Ulazi u stanju 1)

- 2.4. Nadomjesna shema kada su ulazi u stanju 1

- 2.5. Video prikaz integrirani sklopovi skupine TTL

- 2.6. NE sklop u skupini CMOS - ulaz u stanju 0

- 2.7. NE sklop u skupini CMOS - ulaz u stanju 1

- 2.8. NE sklop u skupini MOS - ulaz u stanju 0

- 2.9. NE sklop u skupini MOS - ulaz u stanju 1

- 2.10. Video Integrirani sklopovi skupine CMOS i MOS

- 3. Međusobno spajanje sklopova različitih skupina

1. Karakteristične veličine integrianih digitalnih sklopova

1.1. Utrošak ili gubitak snage

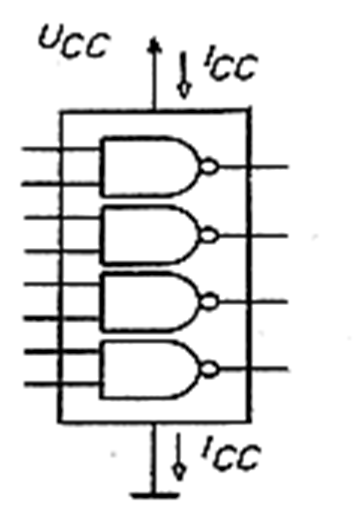

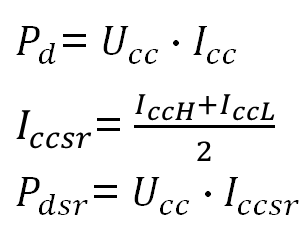

Utrošak ili gubitak snage (engl. power disipation) predstavlja umnožak napona i struje napajanja. Pošto se struje napajanja ICCH i ICCL razlikuju, uzima se njihova srednja vrijednost, a dobiveni umnožak predstavlja prosječnu vrijednost utroška snage.

1.2. Otporno opterećenje prema masi i naponu napajanja

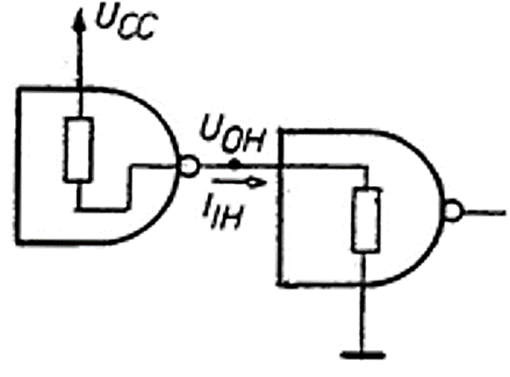

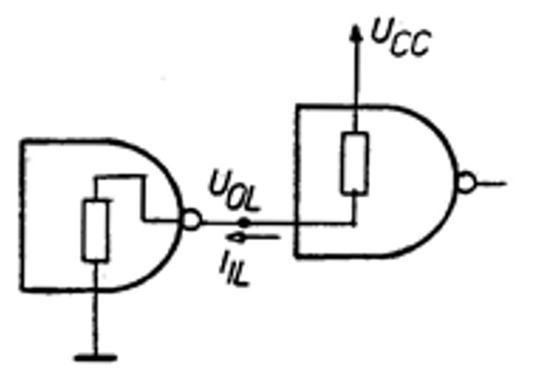

Struja teče u ulaz drugog sklopa. Izlaz prvog sklopa djeluje kao izvor struje za drugi sklop koji predstavlja otporno opterećenje prema masi.

Struja teče iz ulaza drugog sklopa

u izlaz ovog sklopa. Izlaz prvog sklopa djeluje kao ponor struje i vuče struju

iz drugog sklopa koji predstavlja otporno

opterećenje prema naponu napajanja.

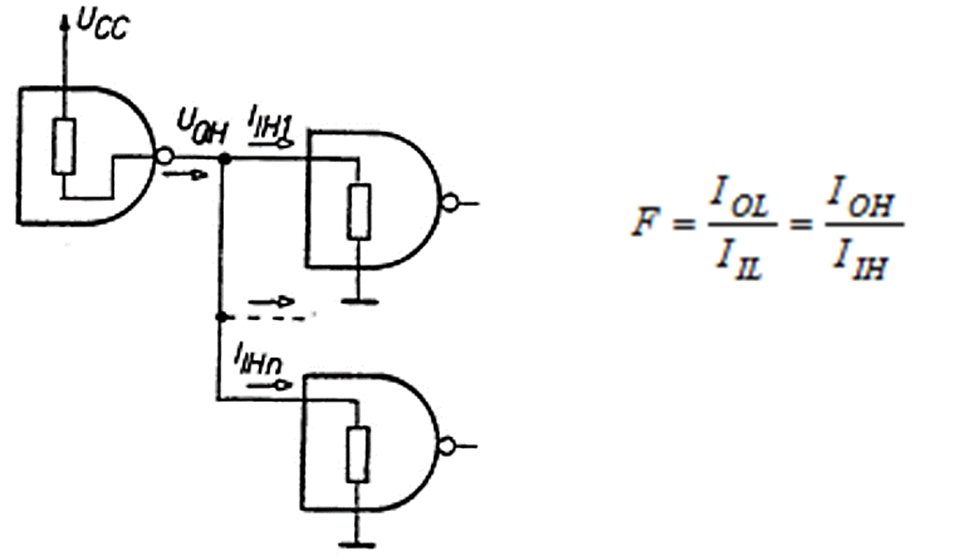

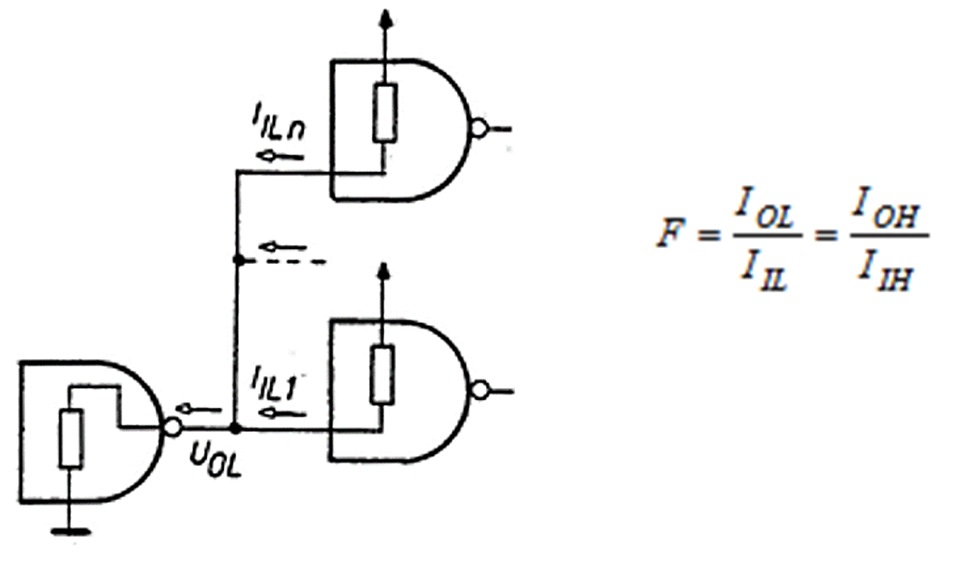

1.3. Faktor razgranjivanja

1.4. Imunost na smetnje

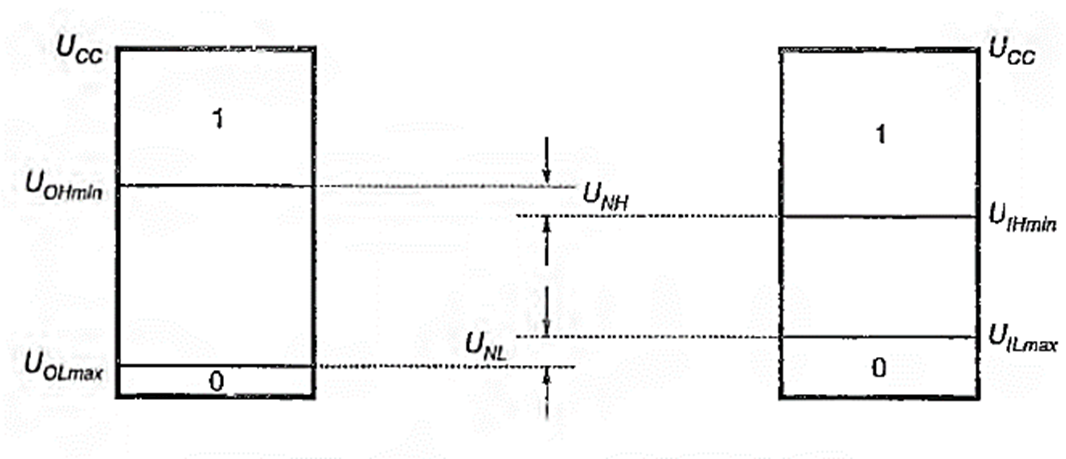

Sposobnost sklopa da na ulazu podnese

određeni iznos napona smetnje naziva

se imunost na smetnje (engl. noise immunity). Mjera imunosti na smetnje iskazuje

se granicom smetnje (engl. noise margin). Granica smetnje je najveći dopušteni

napon na ulazu koji ne izaziva neželjenu promjenu stanja sklopa.

1.5. Brzina rada

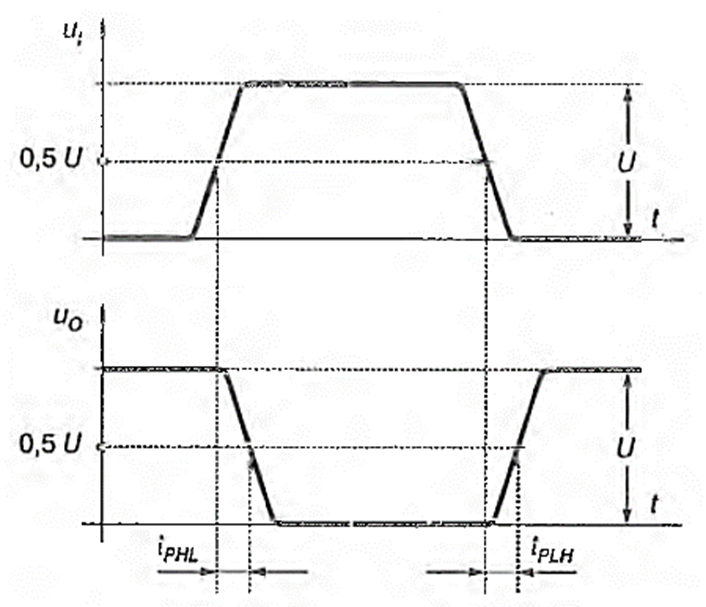

Kad se na ulaz bilo kojeg digitalnog sklopa dovede signal, potrebno je određeno

vrijeme da pod utjecajem tog signala dođe do promjene stanja na izlazu sklopa.

To vrijeme naziva se vrijeme kašnjenja (engl. propagation delay time). Vrijeme

kašnjenja mjeri se najčešće od trenutka kad promjena ulaznog napona dostigne

50% iznosa do trenutka kad promjena izlaznog napona dostigne 50% ukupnog

iznosa.

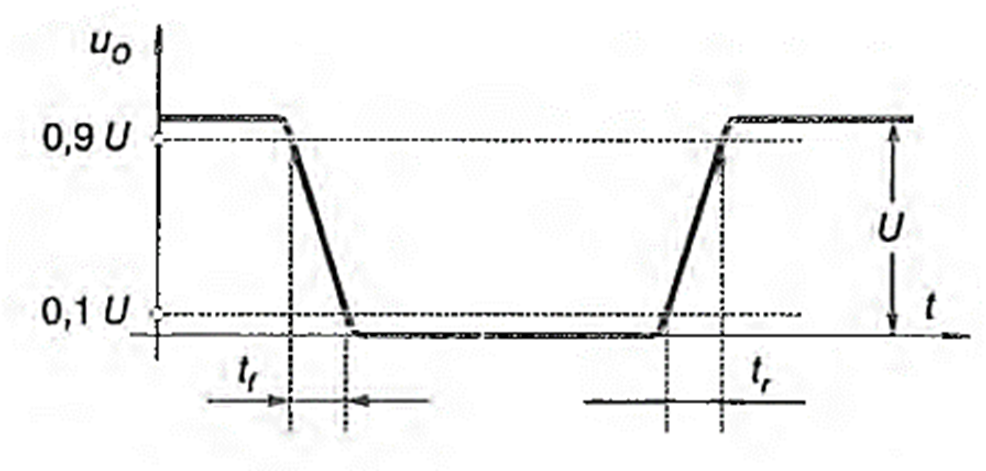

Vrijeme porasta tTLH, odnosno tr (engl. output rise time), vrijeme je potrebno

da se signal promijeni od vrijednosti iz područja niske razine (stanje 0) do vrijednosti

iz područja visoke razine (stanje 1). Vrijeme porasta definira se kao vrijeme

potrebno da signal naraste od 10% do 90% svoje nazivne vrijednosti.

Vrijeme pada tTHL, odnosno tf (engl. output fali time), vrijeme je potrebno da

se signal promijeni od vrijednosti iz područja visoke razine (stanje 1) do vrijednosti

iz područja niske razine (stanje 0). Vrijeme pada definira se kao vrijeme

potrebno da se signal smanji od 90% na 10% svoje nazivne vrijednosti.

1.6. Video prikaz Karakteristične veličine integriranih sklopova

2. Integrirani sklopovi skupina TTL, MOS i CMOS

U potpoglavljima će biti prikazani osnovni sklopovi navedenih skupina, objašnjenja njihovih shema te nadomjesne sheme.

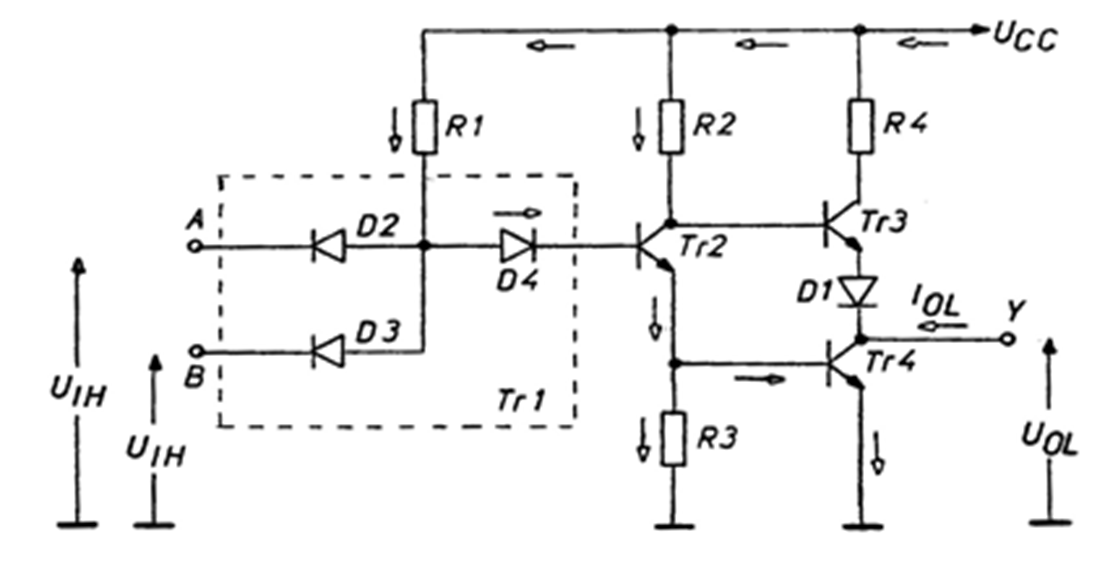

2.1. Osnovni sklop skupine TTL (Ulazi u stanju 0)

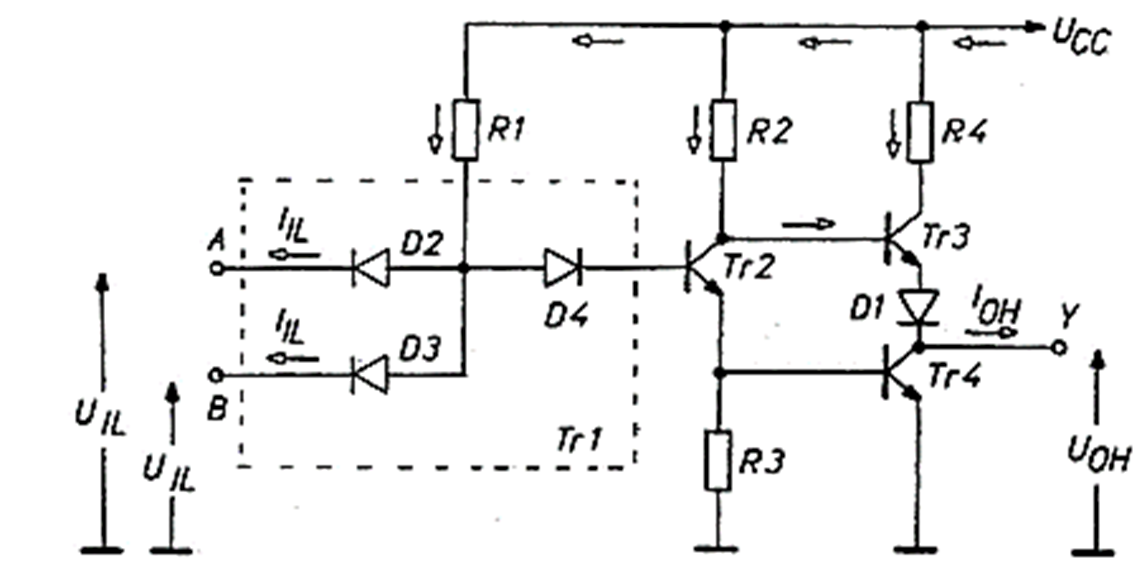

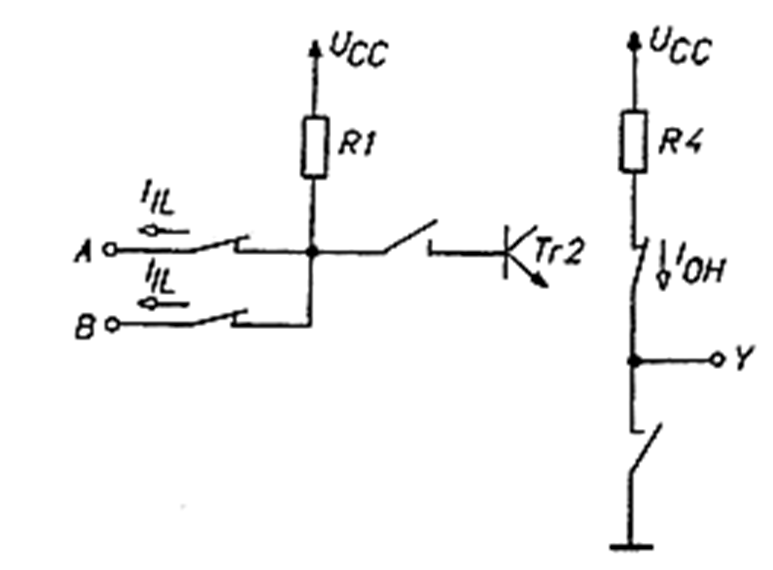

Ulazi sklopa A i B su u stanju logičke 0 (UIL ) . Na katode dioda D2 i D3 je tako dovedena 0 a na njihovim anodama je UCC. S obzirom na to diode D2 i D3 vode i struja iz UCC-a teće prema masi. D4 ne vodi jer sva struja ide preko D2 i D3. Do baze tranzistora Tr2 ne dolazi struja te on ne vodi pa ne vodi ni Tr4. Tr3 vodi jer je UCC spojem s bazom. Preko Tr3 napon UCC dolazi na Y te je izlaz u stanju logičke 1.

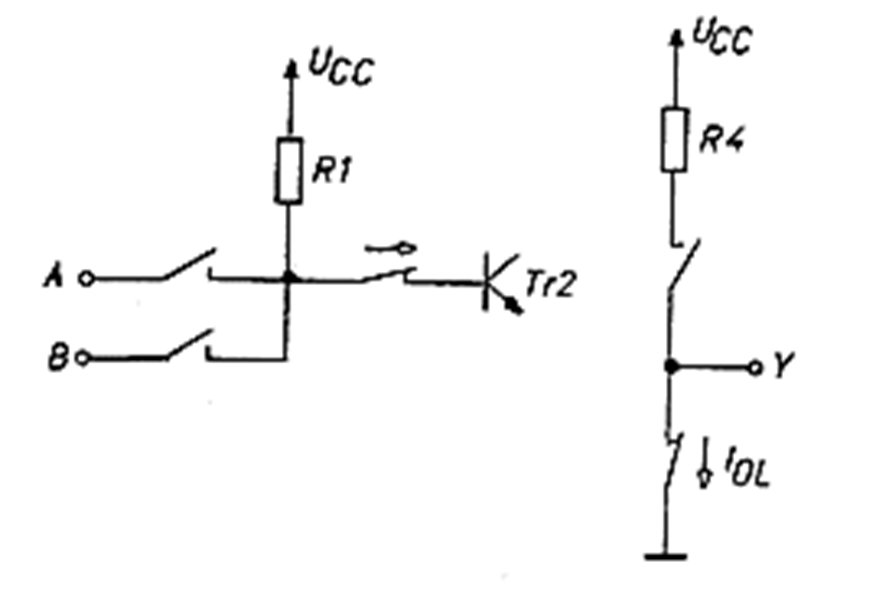

2.2. Nadomjesna shema kada su ulazi u stanju 0

Diode povezane s ulazima A i B vode pa su one nadomještene zatvorenim sklopkama. D4 ne vodi pa je ona predstavljena otvorenom sklopkom. Tr3 vodi pa je on predstavljen zatvorenom sklopkom te je Y spojen direktno na UCC. Tr4 ne vodi pa je predstavljen otvorenom sklopkom.

2.3. Osnovni sklop skupine TTL (Ulazi u stanju 1)

Ulazi sklopa A i B su u stanju logičke 1 (UIH) . Na katode dioda D2 i D3 je tako doveden isti napon kao i na njihovim anodama (UCC). S obzirom da razlika napona katode i anode nije veća od napona praga dioda one ne vode. Dioda D4 u ovom slučaju vodi jer je UCC spojen na njenu anodu. Posljedično i Tr2 vodi i dovodi struju do Tr4 koja također vodi. S obzirom da je UCC preko Tr2 direktno spojen na masu struja na bazi tranzistora Tr3 nije dovoljna da on provede. Y je preko Tr4 direktno spojen s masom.

2.4. Nadomjesna shema kada su ulazi u stanju 1

Diode povezane s ulazima A i B ne vode pa su one nadomještene otvorenim sklopkama. D4 vodi pa je ona predstavljena zatvorenom sklopkom. Tr3 ne vodi pa je on predstavljen otvorenom sklopkom. Tr4 ne vodi pa je predstavljen zatvorenom sklopkom te je Y spojen direktno na masu.

2.5. Video prikaz integrirani sklopovi skupine TTL

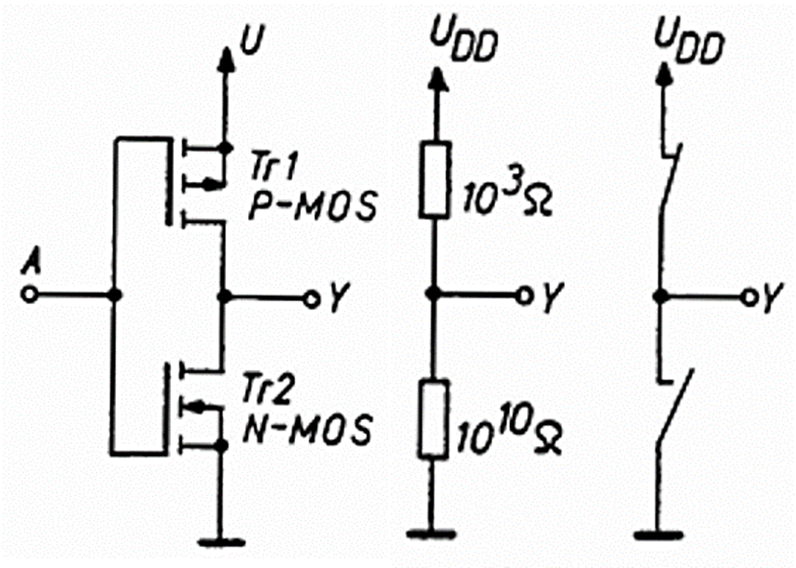

2.6. NE sklop u skupini CMOS - ulaz u stanju 0

Na lijevoj slici je prikazan CMOS NE sklop.

Ako je ulazni napon 0 V (stanje 0 na ulaz A), tranzistor Tr2 ima napon UGS=0 V i zbog toga je u zapiranju s otporom između odvoda i uvoda oko 1010 ohma . Upravljačka elektroda tranzistora Tr1 je za napon UDD na nižem potencijalu od njegova uvoda pa je tranzistor Tr1 u zasićenju s otporom između odvoda i uvoda oko 103 . Izlaz Y je praktički odvojen od zajedničke točke, a spojen na napon napajanja pa je na izlazu stanje 1.

Srednja slika predstavlja nadomjesnu shemu NE sklopa u skupini CMOS prikazanu preko nadomjesnih otpora za ulaz u stanju 0.

Desna slika predstavlja nadomjesnu shemu NE sklopa u skupini CMOS prikazanu preko sklopki za ulaz u stanju 0.

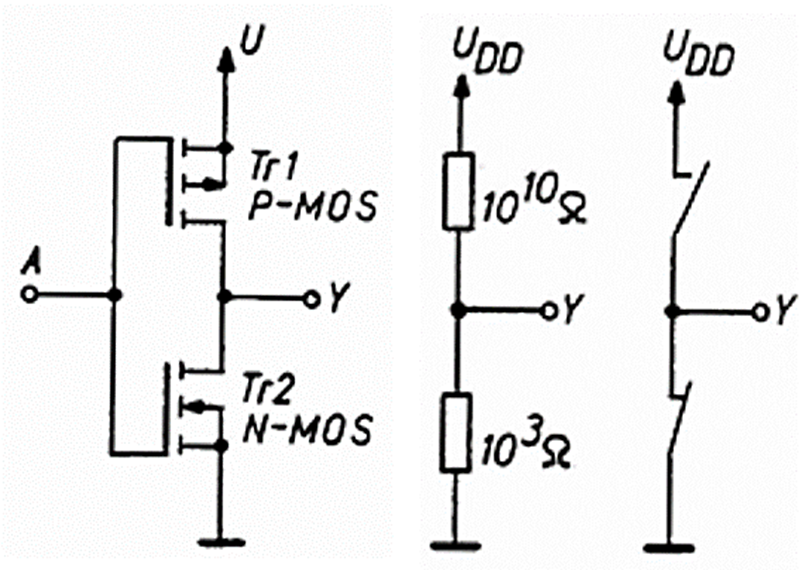

2.7. NE sklop u skupini CMOS - ulaz u stanju 1

Na lijevoj slici je prikazan CMOS NE sklop.

Kad je ulazni napon UDD (stanje 1 na ulazu A), tranzistor Tr1 ima napon UGS=0 V i zbog toga je u zapiranju s otporom između odvoda i uvoda oko 1010 . Upravljačka elektroda tranzistora Tr2 je za napon UDD na pozitivnijem potencijalu od njegova uvoda pa je tranzistor Tr2 u zasićenju s otporom između odvoda i uvoda oko 1010 . Izlaz Y je sada praktički spojen na zajedničku točku, a odspojen od napona napajanja pa je na izlazu stanje 0.

Srednja slika predstavlja nadomjesnu shemu NE sklopa u skupini CMOS prikazanu preko nadomjesnih otpora za ulaz u stanju 1.

Desna slika predstavlja nadomjesnu shemu NE sklopa u skupini CMOS prikazanu preko sklopki za ulaz u stanju 1.

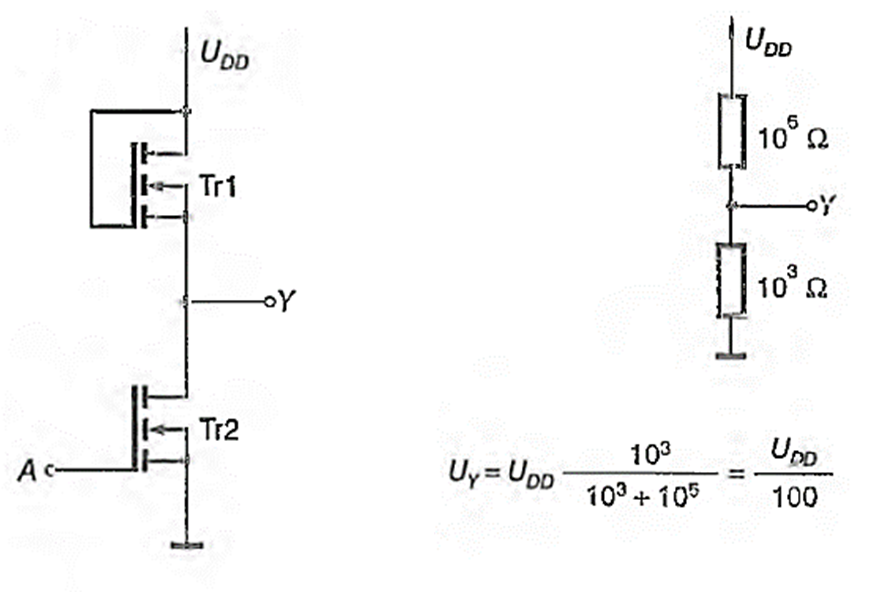

2.8. NE sklop u skupini MOS - ulaz u stanju 0

Tranzistor Tr2 je sklopka čije stanje ovisi o stanju signala na ulazu A. Kada je taj tranzistor u vodljivom stanju, tj. uključena sklopka, njegov otpor iznosi oko 1 kΩ. Kada je tranzistor Tr2 nevodljiv, tj. isključena sklopka, njegov otpor je oko 1010 Ω. Tranzistor Tr1 ima ulogu otpornika (engl. load MOSFET). Njegova upravljaĉka elektroda stalno je spojena na napon napajanja UDD. Zbog toga je taj tranzistor stalno u vodljivom stanju. Izveden je tako da njegov otpor u vodljivom stanju iznosi oko 100 kΩ. (ima uži vodljivi kanal).

Kada je na ulazu A napon UDD, tj. logičko stanje 1, tranzistor Tr2 je u stanju vođenja i ima

otpor iznosa oko 1 kΩ. Odnos otpora djelitelja koji čine tranzistori Tr1 i Tr2 takav je da izlazni

napon približno iznosi stoti dio napona napajanja, što znači da je izlaz u stanju 0.

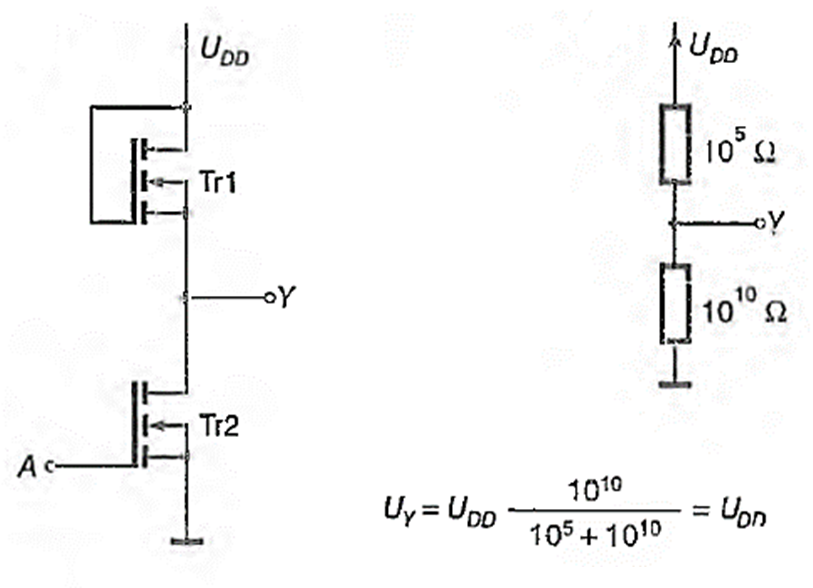

2.9. NE sklop u skupini MOS - ulaz u stanju 1

Tranzistor Tr2 je sklopka čije

stanje ovisi o stanju signala na ulazu A. Kada je taj tranzistor u vodljivom stanju, tj. uključena

sklopka, njegov otpor iznosi oko 1 kΩ. Kada je tranzistor Tr2 nevodljiv, tj. isključena sklopka,

njegov otpor je oko 1010 Ω. Tranzistor Tr1 ima ulogu otpornika (engl. load MOSFET). Njegova

upravljaĉka elektroda stalno je spojena na napon napajanja UDD. Zbog toga je taj tranzistor stalno u

vodljivom stanju. Izveden je tako da njegov otpor u vodljivom stanju iznosi oko 100 kΩ. (ima uži

vodljivi kanal).

Kada je na ulazu A napon 0 V, tj. logičko stanje 0, tranzistor Tr2 je u stanju zapiranja i

ima vrlo veliki otpor, oko 1010 Ω. Tranzistori Tri i Tr2 čine djelitelj napona u kojem je na

tranzistoru Tr2 praktički sav priključeni napon jer je njegov otpor oko 105

puta veći od otpora

tranzistora Tr1. Zbog toga je izlazni napon praktički jednak naponu UDD pa je izlaz u logičkom

stanju 1.

2.10. Video Integrirani sklopovi skupine CMOS i MOS

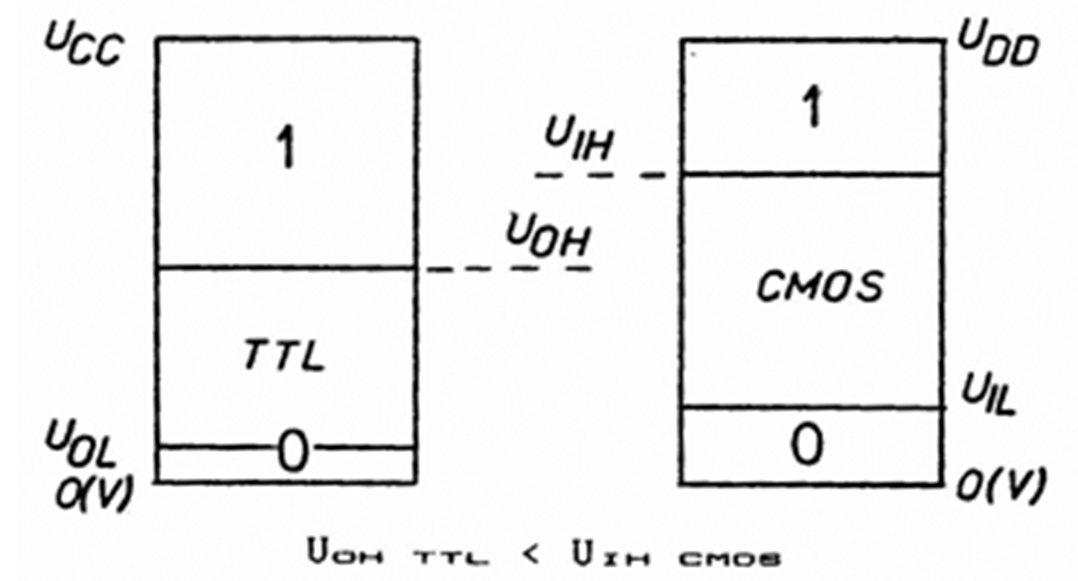

3. Međusobno spajanje sklopova različitih skupina

Prilikom međusobnog spajanja izlaza sklopova skupine TTL i ulaza sklopova

CMOS osnovnu teškoću predstavlja razina izlaznog napona sklopova TTL kod

stanja 1. Ona je čak i kod istovjetnog napona napajanja (5 V) nedovoljna za

većinu sklopova iz skupine CMOS. Izuzetak su sklopovi podskupina

74HCT i 74ACT koji su kompatibilni sa sklopovima TTL.

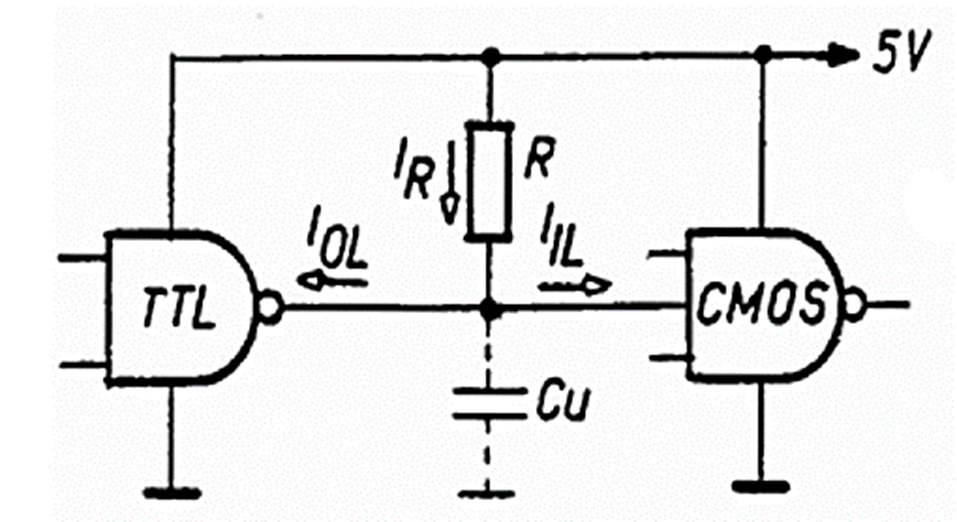

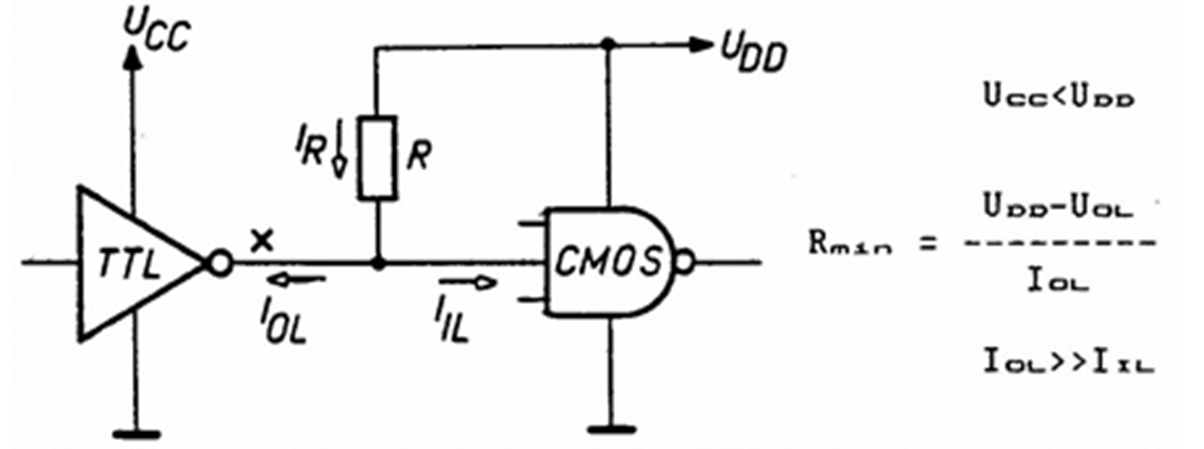

3.1. Jednak napon napajanja TTL i CMOS

Kad je napon napajanja sklopova TTL i CMOS jednak (5 V), međusobno spajanje moguće je ostvariti spajanjem otpornika R između spojišta izlaza sklopa

TTL i ulaza sklopa CMOS i napona napajanja.

Zbog vanjskog otpornika poželjno je koristiti TTL sklopove s otvorenim kolektorom, a sam otpor R, reda veličine kilooma, podiže razinu izlaznog napona sklopa TTL.

Dodavanjem vanjskog otpornika R reda veličine kilooma, podiže se razina izlaznog napona sklopa TTL. S obzirom na dodavanje vanjskog otpornika mogu se koristiti sklopovi TTL s otvorenim kolektorom. Sa stajališta opterećenja izlaza sklopa TTL u stanju niske razine (stanje 0) i opterećenja izvora napajanja, povoljnije je za otpor R izabrati veću vrijednost. Međutim, ulazna kapacitivnost sklopova CMOS kod stanja visoke izlazne razine (stanjel) nabija se preko otpora R. Uz veliku vrijednost otpora R dolazi do znatnog smanjenja brzine rada. Zato se, ako je u sustavu bitno zadržati veću brzinu rada, može koristiti i manja vrijednost, vodeći računa o tome da se izlaz sklopa TTL u stanju niske razine ne optereti strujom većom od I0L.

3.2. Različiti naponi napajanja TTL i CMOS

Uporaba sklopova s otvorenim kolektorom nužna je kad su naponi napajanja

sklopova TTL i CMOS različiti. No tada se moraju koristiti takvi

sklopovi s otvorenim kolektorom kod kojih je moguće vanjski otpornik spojiti na

napon veći od 5 V, tj. sklopovi kod kojih je moguće U0H> Ucc (npr. 7405 ili 7406).

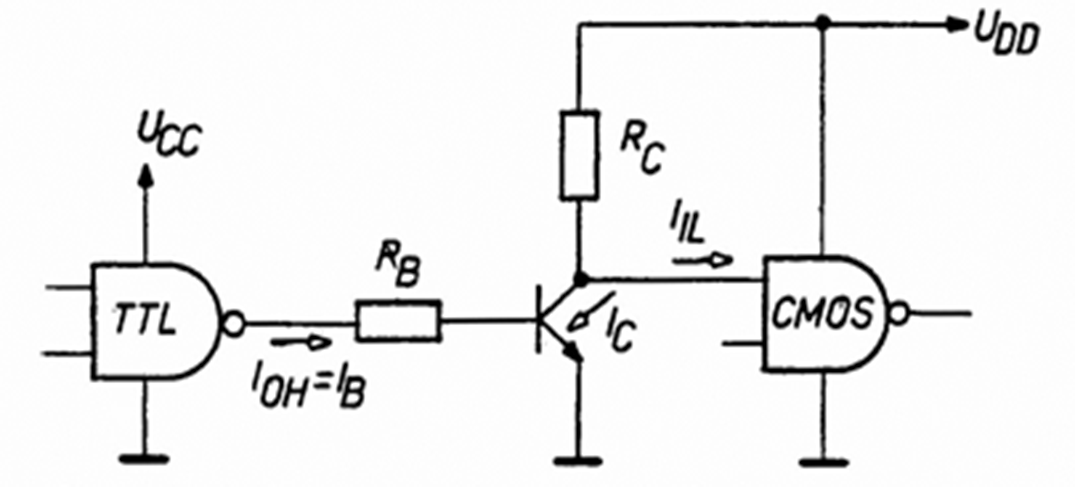

3.3. Tranzistorska sklopka

Za međusobno spajanje sklopova skupina TTL i CMOS može se koristiti i

tranzistorska sklopka.

Kad je izlaz sklopa TTL u stanju visoke razine (stanjel), teče iz njega struja

koja dovodi tranzistor u zasićenje pa je na ulazu sklopa CMOS stanje niske razine

(stanje 0). Otpornik RB treba imati takvu vrijednost koja će dati potrebnu struju

baze za vođenje tranzistora, ali koja neće preopteretiti izlaz sklopa TTL.

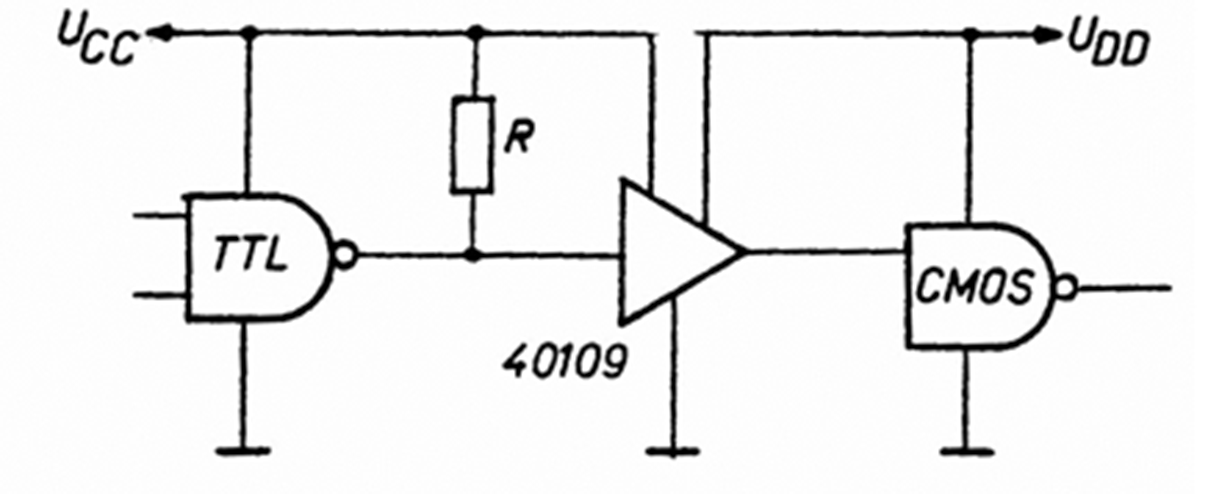

3.4. Integrirani sklopovi za pomak razine

Za međusobno povezivanje ulaza sklopova CMOS sa izlazom sklopova TTL koriste se i integrirani sklopovi za pomak razine (engl. level translator). Integrirani sklop 40109 ima tri izvoda za napajanje (slika ispod). Jedan je zajednički (uzemljen), a dva napajanje UCC, odnosno UDD. Otpornik R na izlazu TTL sklopa diže izlazni napon u stanju 1 s iznosa 2,4 V na približno 5 V potreban za ulaz sklopa 40109. Sklop 40109 daje na izlazu u stanju 1 napon potreban za ulaz sklopova CMOS.