VHDL

| Sito: | CARNET - Arhiva 2021 Loomen |

| Corso: | Digitalna logika |

| Libro: | VHDL |

| Stampato da: | Invitado |

| Data: | Tuesday, 21 April 2026, 00:55 |

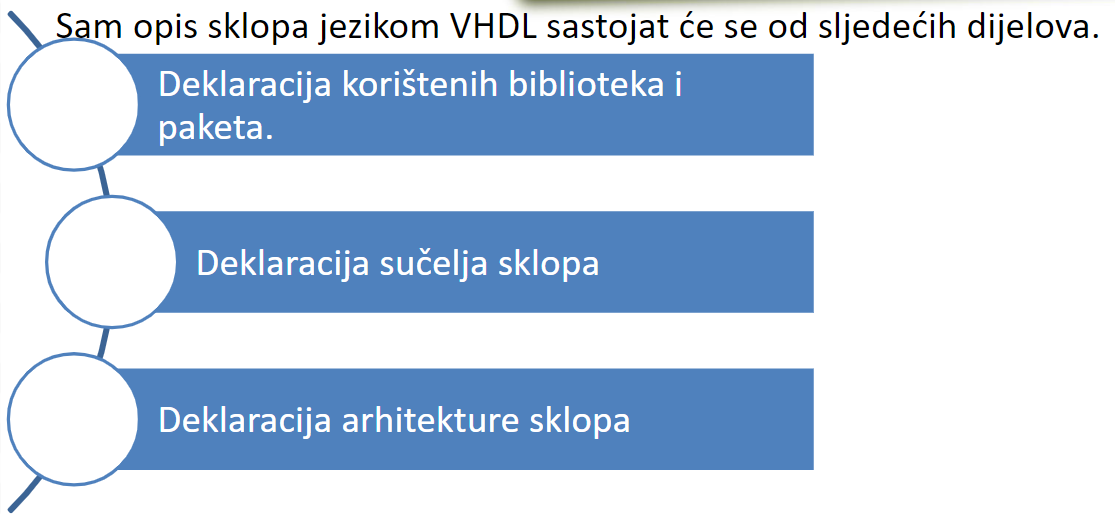

1. Osnovne sastavnice VHDL programa

1.1. Deklaracija korištenih biblioteka i paketa

Standard paket je predefiniran u kompajleru.

Definirani tipovi uključuju: bit bit_vector typical signals

integer natural positive typical variables

boolean string character typical variables

real time delay_length typical variablesstd_logic_1164 paket pruža pojačane signalne tipove Definirani tipovi uključuju: std_ulogic std_ulogic_vector std_logic std_logic_vector

TYPE std_ulogic => ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

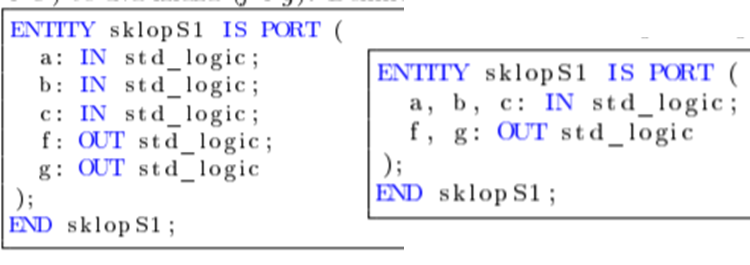

);1.2. Deklaracija sučelja sklopa

Entity deklaracija prikazuje ulaze i izlazne portove dizajna.

Port u VHDL-u je veza VHDL dizajn entiteta s vanjskim svijetom. Smjer ili smjerovi u kojem portovi rade se naziva mod. VHDL port može imati jedan od 4 moda: IN (samo ulaz), OUT (samo izlaz), INOUT (dvosmjerno), i BUFFER (izlaz s povratnom vezom iz izlaza natrag prema dizajn entitetu). Mod porta je deklariran u portovima entity deklaracije.

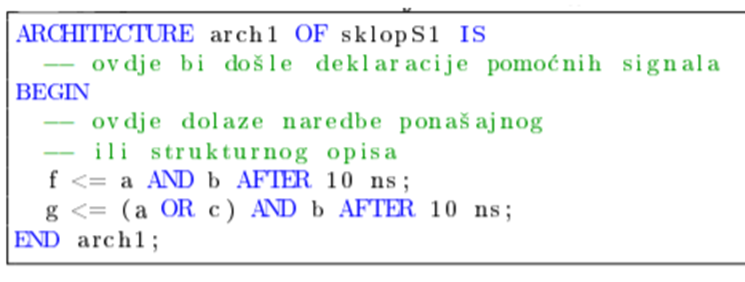

1.3. Deklaracija arhitekture sklopa

Arhitektura daje detaljan opis odnosa između ulaza i izlaza.

Signal je kao unutarnja žica koja spaja dvije ili više točaka unutar tijela arhitekture. Deklarira se prije BEGIN dijela arhitekture i globalna je varijabla za arhitekturu. Njena vrijednost se dodijeljuje pomoću <= operatora. Varijabla je dio radne memorije, lokalna je za svaki proces. Deklarira se prije BEGIN dijela procesa i dodijeljuje se pomoću := operatora.

2. Modeli VHDL programa

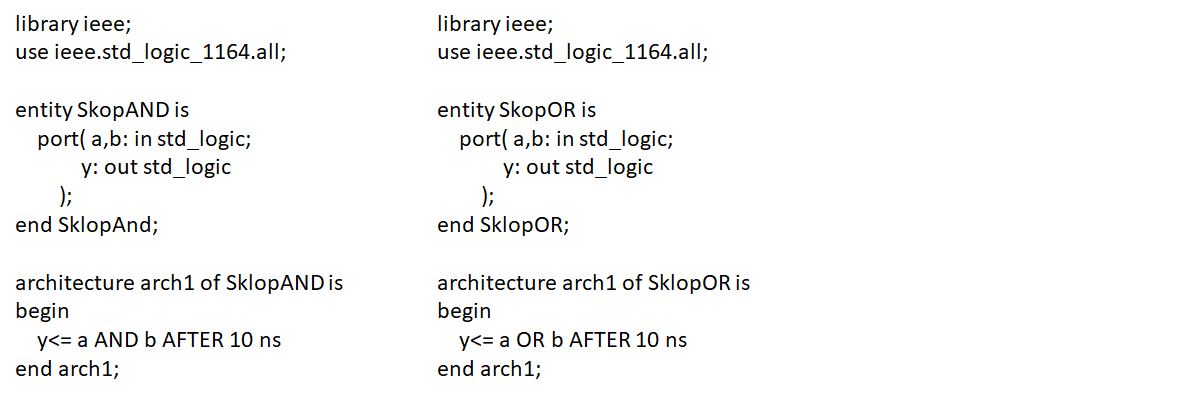

2.1. Model toka podataka

Model toka podataka (engl. dataflow model) je model sklopa kod kojega pišemo naredbe koje kombiniraju ulazne signale (i eventualno pomoćne signale) uporabom naredbi dodjeljivanja vrijednosti signalima i tako određuje vrijednosti izlaza sklopa.

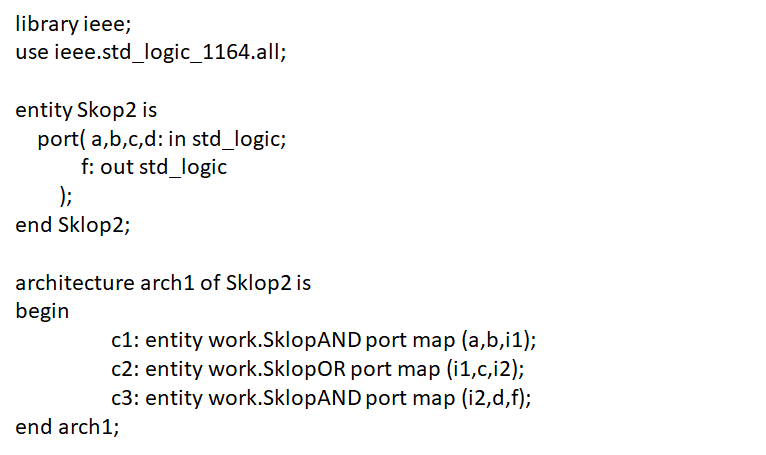

2.2. Strukturni model

Strukturni model (engl. structural model) je model sklopa koji sklop opisuje pozivajući se na njegovu građu te način na koji su jednostavnije komponente od kojih je sklop izgrađen povezane s ulazima, povezane međusobno te povezane s izlazima modeliranog sklopa.

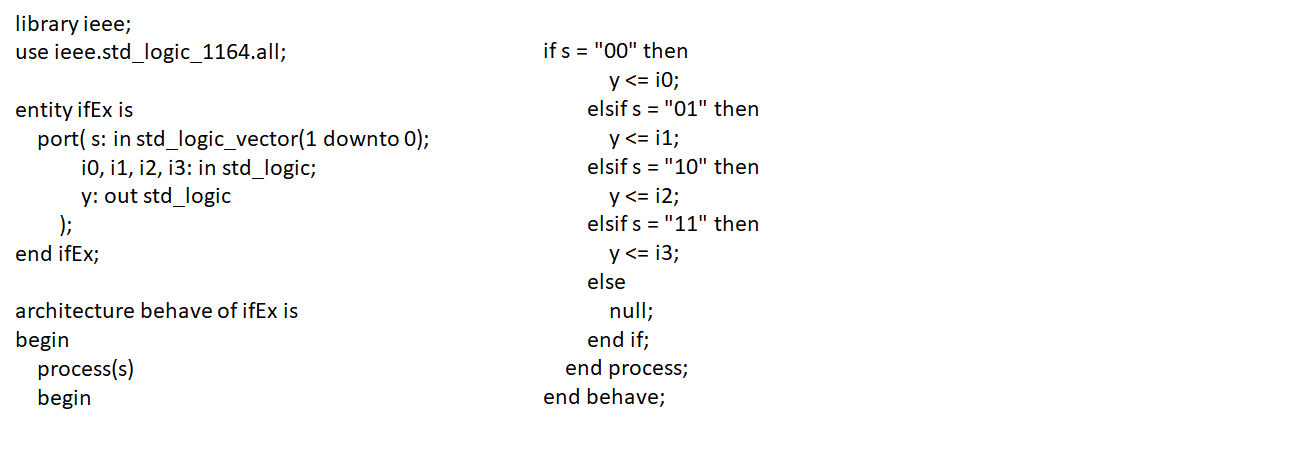

2.3. Funkcijski model

Funkcijski model (zovemo ga još i ponašajni model, engl. behavioral model) je model sklopa kod kojega funkcionalnost sklopa najčešće ne opisujemo oslanjajući se logičke operatore koji bi oslikavali način na koji se ulazi transformiraju u izlaze već pišemo algoritam koji nam ne govori kako bi sklop trebalo sintetizirati već samo navodi kako se ulazi preslikavaju u izlaze.